# Implications of Slow or Floating CMOS Inputs

# ABSTRACT

In recent years, CMOS (AC/ACT, AHC/AHCT, ALVC, CBT, CBTLV, HC/HCT, LVC, LV/LV-A) and BiCMOS (ABT, ALVT, BCT, FB, GTL, and LVT) logic families have further strengthened their position in the semiconductor market. New designs have adopted both technologies in almost every system that exists, whether it is a PC, a workstation, or a digital switch. The reason is obvious: power consumption is becoming a major issue in today's market. However, when designing systems using CMOS and BiCMOS devices, one must understand the characteristics of these families and the way inputs and outputs behave in systems. It is very important for the designer to follow all rules and restrictions that the manufacturer requires, as well as to design within the data-sheet specifications. Because data sheets do not cover the input behavior of a device in detail, this application report explains the input characteristics of CMOS and BiCMOS families in general. It also explains ways to deal with issues when designing with families in which floating inputs are a concern. Understanding the behavior of these inputs results in more robust designs and better reliability.

# Contents

| 1 | Characteristics of Slow or Floating CMOS Inputs     | 2  |

|---|-----------------------------------------------------|----|

|   | Slow Input Edge Rate                                |    |

| 3 | Recommendations for Designing More-Reliable Systems | 5  |

|   | Bus-Hold Circuits                                   |    |

| 5 | Summary                                             | 12 |

### List of Figures

| 1  | Input Structures of ABT and LVT/LVC Devices                                                             | 2  |

|----|---------------------------------------------------------------------------------------------------------|----|

| 2  | Supply Current Versus Input Voltage (One Input)                                                         | 2  |

| 3  | Input Transition Rise or Fall Rate as Specified in Data Sheets                                          | 3  |

| 4  | Input/Output Model                                                                                      | 3  |

| 5  | Examples of Supply-Current Change of the Input at TTL Level as Specified in Data Sheets                 | 4  |

| 6  | Supply Current Versus Input Voltage (36 Inputs)                                                         | 4  |

| 7  | Typical Bidirectional Bus                                                                               | 5  |

| 8  | Inactive-Bus Model With a Defined Level                                                                 | 6  |

| 9  | Typical Bus-Hold Circuit                                                                                | 7  |

| 10 | Stand-Alone Bus-Hold Circuit (SN74ACT107x)                                                              | 7  |

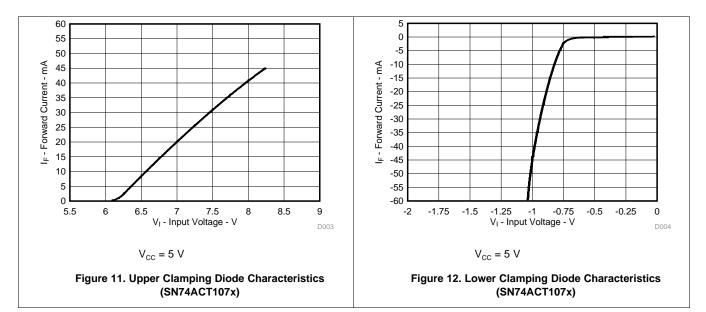

| 11 | Upper Clamping Diode Characteristics (SN74ACT107x)                                                      | 8  |

| 12 | Lower Clamping Diode Characteristics (SN74ACT107x)                                                      | 8  |

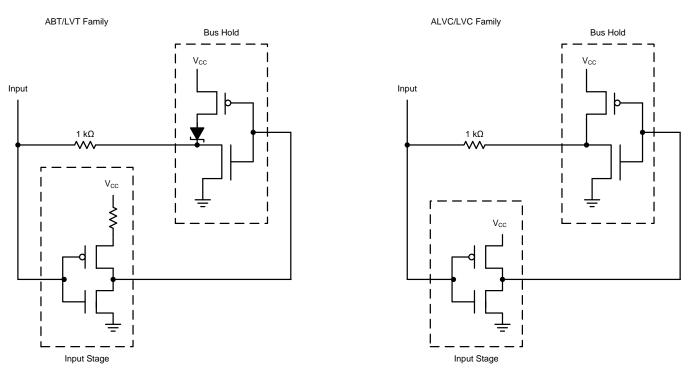

| 13 | Input Structure of ABT/LVT and ALVC/LVC Families With Bus-Hold Circuit                                  | 9  |

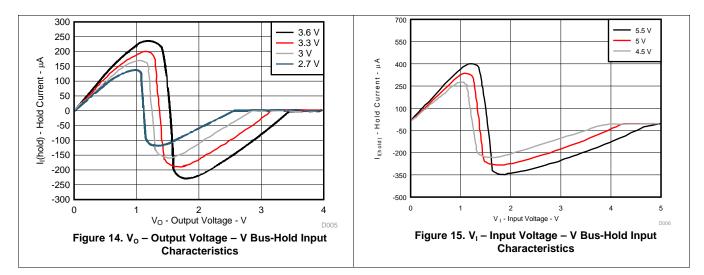

| 14 | Vo – Output Voltage – V Bus-Hold Input Characteristics                                                  | 9  |

| 15 | V <sub>I</sub> – Input Voltage – V Bus-Hold Input Characteristics                                       | 9  |

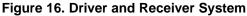

| 16 | Driver and Receiver System                                                                              | 10 |

| 17 | Driver Switching From High to Low Output Waveforms of Driver With and Without Receiver Bus-Hold Circuit | 10 |

| 18 | Driver Switching From Low to High Output Waveforms of Driver With and Without Receiver Bus-Hold Circuit | 10 |

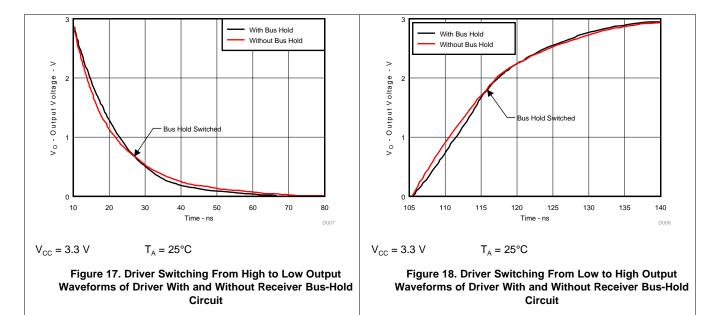

| 19 | Bus-Hold Circuit Supply Current Versus Input Voltage                                                    | 11 |

|    |                                                                                                         |    |

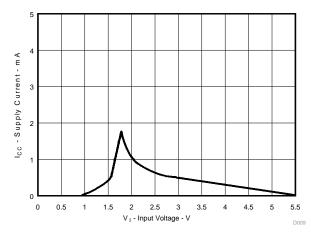

| 20 | Power Plot of the Input Power With Bus Hold at Different Frequencies    | 11 |

|----|-------------------------------------------------------------------------|----|

| 21 | Power Plot of the Input Power Without Bus Hold at Different Frequencies | 11 |

| 22 | Example of Data-Sheet Minimum Specification for Bus Hold                | 11 |

# Trademarks

Widebus is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

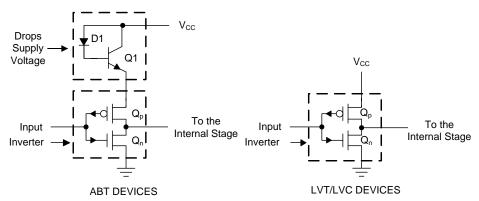

# 1 Characteristics of Slow or Floating CMOS Inputs

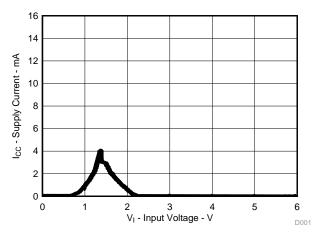

Both CMOS and BiCMOS families have a CMOS input structure. This structure is an inverter consisting of a p-channel to VCC and an n-channel to GND as shown in Figure 1. With low-level input, the P-channel transistor is on and the N-channel is off, causing current to flow from  $V_{CC}$  and pulling the node to a high state. With high-level input, the n-channel transistor is on, the P-channel is off, and the current flows to GND, pulling the node low. In both cases, no current flows from  $V_{CC}$  to GND. However, when switching from one state to another, the input crosses the threshold region, causing the N-channel and the P-channel to turn on simultaneously, generating a current path between  $V_{CC}$  and GND. This current surge can be damaging, depending on the length of time that the input is in the threshold region (0.8 to 2 V). The supply current ( $I_{CC}$ ) can rise to several milliamperes per input, peaking at approximately 1.5-V V<sub>1</sub> (see Figure 2). This is not a problem when switching states within the data-sheet-specified input transition time limit specified in the recommended operating conditions table for the specific devices. Examples are shown in Figure 3.

Figure 1. Input Structures of ABT and LVT/LVC Devices

$V_{cc} = 5 V$   $T_{A} = 25^{\circ}C$ One Bit is Driven From 0 V to 6 V

# Figure 2. Supply Current Versus Input Voltage (One Input)

#### Recommended Operating Conditions (1)

|                       | 1 0                                      |                       |                               | MIN                       | MAX  | UNIT |  |

|-----------------------|------------------------------------------|-----------------------|-------------------------------|---------------------------|------|------|--|

|                       | Input transition rise or fall rate       | ABT octals            |                               |                           | 5    |      |  |

|                       |                                          | ABT Widebus™ and Wide | ebus+™                        |                           | 10   |      |  |

|                       |                                          | AHC, AHCT             |                               |                           | 20   |      |  |

|                       |                                          | FB                    |                               |                           | 10   |      |  |

| $\Delta t / \Delta v$ |                                          | LVT, LVC, ALVC, ALVT  |                               |                           | 10   | ns/V |  |

|                       |                                          | LV                    |                               |                           | 100  |      |  |

|                       |                                          | LV                    |                               | $V_{CC}$ = 2.3 V to 2.7 V |      | 200  |  |

|                       |                                          |                       | LV-A                          | $V_{CC} = 3 V$ to 3.6 V   |      | 100  |  |

|                       |                                          |                       | $V_{\rm CC}$ = 4.5 V to 5.5 V |                           | 20   |      |  |

|                       | Input transition (rise and fall)<br>time |                       | $V_{CC} = 2 V$                |                           | 1000 | ns   |  |

| t                     |                                          |                       | $V_{CC} = 4.5 V$              |                           | 500  |      |  |

|                       |                                          |                       | $V_{CC} = 6 V$                |                           | 400  |      |  |

(1) Refer to the latest TI data sheets for device specifications.

# Figure 3. Input Transition Rise or Fall Rate as Specified in Data Sheets

# 2 Slow Input Edge Rate

With increased speed, logic devices have become more sensitive to slow input edge rates. A slow input edge rate, coupled with the noise generated on the power rails when the output switches, can cause excessive output errors or oscillations. Similar situations can occur if an unused input is left floating or is not actively held at a valid logic level.

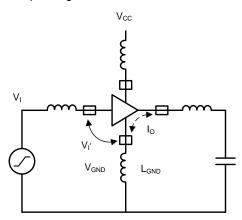

These functional problems are due to voltage transients induced on the device's power system as the output load current ( $I_0$ ) flows through the parasitic lead inductances during switching (see Figure 4). Because the device's internal power-supply nodes are used as voltage references throughout the integrated circuit, inductive voltage spikes,  $V_{GND}$ , affect the way signals appear to the internal gate structures. For example, as the voltage at the device's ground node rises, the input signal,  $V_1$ , appears to decrease in magnitude. This undesirable phenomenon can then erroneously change the output if a threshold violation occurs.

In the case of a slowly rising input edge, if the change in voltage at GND is large enough, the apparent signal,  $V_i$ , at the device appears to be driven back through the threshold and the output starts to switch in the opposite direction. If worst-case conditions prevail (simultaneously switching all of the outputs with large transient load currents), the slow input edge is repeatedly driven back through the threshold, causing the output to oscillate. Therefore, the maximum input transition time of the device should not be violated, so no damage to the circuit or the package occurs.

Figure 4. Input/Output Model

Slow Input Edge Rate

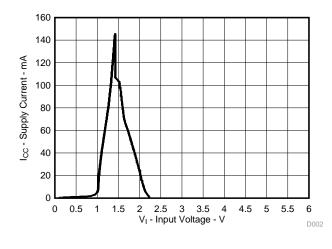

If a voltage between 0.8 V and 2 V is applied to the input for a prolonged period of time, this situation becomes critical and should not be ignored, especially with higher bit count and more dense packages (SSOP, TSSOP). For example, if an 18-bit transceiver has 36 I/O pins floating at the threshold, the current from V<sub>CC</sub> can be as high as 150 mA to 200 mA. This is approximately 1 W of power consumed by the device, which leads to a serious overheating problem. This continuous overheating of the device affects its reliability. Also, because the inputs are in the threshold region, the outputs tend to oscillate, resulting in damage to the internal circuit over a long period of time. The data sheet shows the increase in supply current ( $\Delta$ I<sub>CC</sub>) when the input is at a TTL level [for ABT V<sub>I</sub> = 3.4 V,  $\Delta$ I<sub>CC</sub> = 1.5 mA (see Figure 5)]. This becomes more critical when the input is in the threshold region as shown in Figure 6.

These characteristics are typical for all CMOS input circuits, including microprocessors and memories.

For CBT or CBTLV devices, this applies to the control inputs. For FB and GTL devices, this applies to the control inputs and the TTL ports only.

|                      |                            |                                   |                                          |                                 | MIN | MAX | UNIT |

|----------------------|----------------------------|-----------------------------------|------------------------------------------|---------------------------------|-----|-----|------|

|                      | ABT, AHCT                  | $V_{CC} = 5.5 V,$                 | One input at 3.4 V,                      | Other inputs at $V_{cc}$ or GND |     | 1.5 |      |

| ΔI <sub>CC</sub> (2) | CBT<br>Control<br>inputs   | V <sub>CC</sub> = 5.5 V,          | One input at 3.4 V,                      | Other inputs at $V_{cc}$ or GND |     | 2.5 | mA   |

| ΔI <sub>CC</sub> (2) | CBTLV<br>Control<br>inputs | V <sub>CC</sub> = 3.6 V,          | One input at 3 V,                        | Other inputs at $V_{cc}$ or GND |     | 750 | μA   |

|                      | LVC                        |                                   | One input at V <sub>cc</sub> -<br>0.6 V, | Other inputs at $V_{cc}$ or GND |     | 0.2 |      |

| ΔI <sub>CC</sub> (2) | LVC, ALVC,<br>LV           | $V_{cc} = 3 V \text{ to } 3 6 V,$ |                                          |                                 |     | 0.5 | mA   |

Electrical Characteristics over recommended operating free-air temperature range (unless otherwise noted) (1)

(1) Refer to the latest TI data sheets for device specifications.

(2) This is the increase in supply current for each input that is at the specified TTL voltage level rather than  $V_{cc}$  or GND.

### Figure 5. Examples of Supply-Current Change of the Input at TTL Level as Specified in Data Sheets

$V_{CC} = 5 V$   $T_A = 25^{\circ}C$ All 36 Bits are Driven From 0 V to 6 V

# Figure 6. Supply Current Versus Input Voltage (36 Inputs)

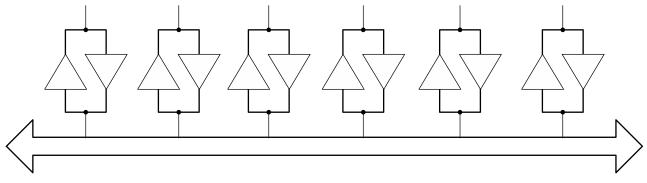

As long as the driver is active in a transmission path or bus, the receiver's input is always in a valid state. No input specification is violated as long as the rise and fall times are within the data-sheet limits. However, when the driver is in a high-impedance state, the receiver input is no longer at a defined level and tends to float. This situation can worsen when several transceivers share the same bus. Figure 7 is an example of a typical bus system. When all transceivers are inactive, the bus-line levels are undefined. When a voltage that is determined by the leakage currents of each component on the bus is reached, the condition is known as a *floating state*. The result is a considerable increase in power consumption and a risk of damaging all components on the bus. Holding the inputs or I/O pins at a valid logic level when they are not being used or when the part driving them is in the high-impedance state is recommended.

Figure 7. Typical Bidirectional Bus

# 3 Recommendations for Designing More-Reliable Systems

# 3.1 Bus Control

The simplest way to avoid floating inputs in a bus system is to ensure that the bus always is either active or inactive for a limited time when the voltage buildup does not exceed the maximum  $V_{IL}$  specification (0.8 V for TTL-compatible input). At this voltage, the corresponding  $I_{CC}$  value is too low and the device operates without any problem or concern (see Figure 2 and Figure 4).

To avoid damaging components, the designer must know the maximum time the bus can float. First, assuming that the maximum leakage current is  $I_{OZ} = 50$  mA and the total capacitance (I/O and line capacitance) is C = 20 pF, the change in voltage with respect to time on an inactive line that exceeds the 0.8-V level can be calculated as shown in Equation 1.

$$\Delta V / \Delta t = \frac{I_{OZ}}{C} = \frac{50 \ \mu A}{20 \ pF} = 2.5 \ V / \mu s$$

(1)

5

The permissible floating time for the bus in this example should be reduced to 320 ns maximum, which ensures that the bus does not exceed the 0.8-V level specified. The time constant does not change when multiple components are involved because their leakage currents and capacitances are summed.

The advantage of this method is that it requires no additional cost for adding special components. Unfortunately, this method does not always apply because buses are not always active.

# 3.2 Pull-up or Pull-down Resistors

When buses are disabled for more than the maximum allowable time, other ways should be used to prevent components from being damaged or overheated. A pull-up or a pull-down resistor to  $V_{cc}$  or GND, respectively, should be used to keep the bus in a defined state. The size of the resistor plays an important role and, if its resistance is not chosen properly, a problem may occur. Usually, a 1-k $\Omega$  to 10-k $\Omega$  resistor is recommended. The maximum input transition time must not be violated when selecting pull-up or pull-down resistors (see Figure 3). Otherwise, components may oscillate, or device reliability may be affected.

(4)

(5)

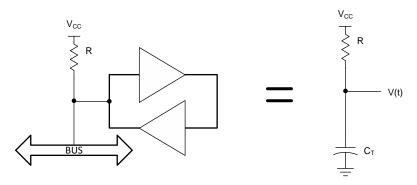

Figure 8. Inactive-Bus Model With a Defined Level

Assume that an active-low bus goes to the high-impedance state as modeled in Figure 8.  $C_T$  represents the device plus the bus-line capacitance and R is a pull-up resistor to V<sub>CC</sub>. The value of the required resistor can be calculated as shown in Equation 2.

$$V(t) = V_{CC} - \left(e^{-t/RC_{T}} \left(V_{CC} - V_{i}\right)\right)$$

where

- V(t) = 2 V, minimum voltage at time t

- V<sub>i</sub> = 0.5 V, initial voltage

- V<sub>cc</sub> = 5 V

- C<sub>T</sub> = total capacitance

- R = pull-up resistor

- t = maximum input rise time as specified in the data sheets (see Figure 3).

(2)

Solving for R, the equation becomes:

$$\mathsf{R} = \frac{\mathsf{t}}{\mathsf{0.4} \times \mathsf{C}_{\mathsf{T}}} \tag{3}$$

For multiple transceivers on a bus:

$$\mathsf{R} = \frac{\mathsf{t}}{\mathsf{0.4} \times \mathsf{C} \times \mathsf{N}}$$

where

- C = individual component and trace capacitance

- N = number of components connected to the bus

Assuming that there are two components connected to the bus, each with a capacitance C = 15 pF, requiring a maximum rise time of 10 ns/V and t = 15-ns total rise time for the input (2 V), the maximum resistor size can be calculated by Equation 5:

$$\mathsf{R} = \frac{15 \text{ ns}}{0.4 \times 15 \text{ pF} \times 2} = 1.25 \text{ k}\Omega$$

This pull-up resistor method is recommended for ac-powered systems; however, it is not recommended for battery-operated equipment because power consumption is critical. Instead, use the bus-hold feature that is discussed in the next section. The overall advantage of using pull-up resistors is that they ensure defined levels when the bus is floating and help eliminate some of the line reflections, because resistors also can act as bus terminations.

# 4 Bus-Hold Circuits

6

The most effective method to provide defined levels for a floating bus is to use Texas Instruments (TI<sup>™</sup>) built-in bus-hold feature on selected families or as an external component like the SN74ACT1071 and SN74ACT1073 (see Table 1).

| BUS HOLD INCORPORATED                |

|--------------------------------------|

| 10-bit bus hold with clamping diodes |

| 16-bit bus hold with clamping diodes |

| All devices                          |

| Selected devices only                |

| TBA (Selected devices only)          |

| All devices                          |

| All devices                          |

|                                      |

Table 1. Devices With Bus Hold

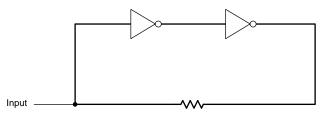

Bus-hold circuits are used in selected TI families to help solve the floating-input problem and eliminate the need for pull-up and pull-down resistors. Bus-hold circuits consist of two back-to-back inverters with the output fed back to the input through a resistor (see Figure 9). To understand how the bus-hold circuit operates, assume that an active driver has switched the line to a high level. This results in no current flowing through the feedback circuit. Now, the driver goes to the high-impedance state and the bus-hold circuit is determined only by the leakage current of the circuit. The same condition applies when the bus is in the low state and then goes inactive.

Figure 9. Typical Bus-Hold Circuit

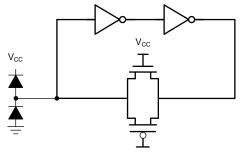

As mentioned previously in this section, TI offers the bus-hold capability as stand-alone 10-bit and 16-bit devices (SN74ACT1071 and SN74ACT1073) with clamping diodes to V<sub>CC</sub> and GND for added protection against line reflections caused by impedance mismatch on the bus. Because purely ohmic resistors cannot be implemented easily in CMOS circuits, a configuration known as a transmission gate is used as the feedback element (see Figure 10). An N-channel and a P-channel are arranged in parallel between the input and the output of the buffer stage. The gate of the N-channel transistor is connected to V<sub>CC</sub> and the gate of the P-channel is connected to GND. When the output of the buffer is high, the p-channel is on, and when the output is low, the N-channel is on. Both channels have a relatively small surface area — the on-state resistance from drain to source,  $R_{dson}$ , is about 5 k $\Omega$ .

Figure 10. Stand-Alone Bus-Hold Circuit (SN74ACT107x)

Assume that in a practical application the leakage current of a driver on a bus is  $I_{OZ} = 10$  mA and the voltage drop across the 5-k $\Omega$  resistance is  $V_D = 0.8$  V (this value is assumed to ensure a defined logic level). Then, the maximum number of components that a bus-hold circuit can handle is calculated by Equation 6:

$$N = \frac{V_D}{I_{OZ} \times R} = \frac{0.8 \text{ V}}{10 \ \mu A \times 5 \ k\Omega} = 16 \text{ components}$$

SCBA004D–July 1994–Revised September 2016 Submit Documentation Feedback

#### Bus-Hold Circuits

www.ti.com

The 74ACT1071 and 74ACT1073 also provide clamping diodes as an added feature to the bus-hold circuit. These diodes are useful for clamping any overshoot or undershoot generated by line reflections. Figure 11 and Figure 12 show the characteristics of the diodes when the input voltage is above  $V_{CC}$  or below GND. At  $V_{I} = -1$  V, the diode can source about 50 mA, which can help eliminate undershoots. This can be very useful when noisy buses are a concern.

TI also offers the bus-hold circuit as a feature added to some of the advanced-family drivers and receivers. This circuit is similar to the stand-alone circuit, with a diode added to the drain of the second inverter (ABT and LVT only, see Figure 13). The diode blocks the overshoot current when the input voltage is higher than  $V_{CC}$  ( $V_1 > V_{CC}$ ), so only the leakage current is present. This circuit uses the device's input stage as its first inverter; a second inverter creates the feedback feature. The calculation of the maximum number of components that the bus-hold circuit can handle is similar to the previous example. However, the advantage of this circuit over the stand-alone bus-hold circuit is that it eliminates the need for external components or resistors that occupy more area on the board. This becomes critical for some designs, especially when wide buses are used. Also, because cost and board-dimension restrictions are a major concern, designers prefer the easy fix: drop-in replaceable parts. TI offers this feature in most of the commonly used functions in several families (refer to Table 1 for more details).

Figure 13. Input Structure of ABT/LVT and ALVC/LVC Families With Bus-Hold Circuit

Figure 14 and Figure 15 show the input characteristics of the bus-hold circuit at 3.3-V and 5-V operations, as the input voltage is swept from 0 to 5 V. These characteristics are similar in behavior to a weak driver. This driver sinks current into the part when the input is low and sources current out of the part when the input is high. When the voltage is near the threshold, the circuit tries to switch to the other state, always keeping the input at a valid level. This is the result of the internal feedback circuit. The plot also shows that the current is at its maximum when the input is near the threshold.  $I_{I(hold)}$  maximum is approximately 25 mA for 3.3-V input and 400 mA for 5-V input.

When multiple devices with bus-hold circuits are driven by a single driver, there may be some concern about the ac switching capability of the driver becoming weaker. As small drivers, bus-hold circuits require an ac current to switch them. This current is not significant when using TI CMOS and BiCMOS families. Figure 16 shows a 4-mA buffer driving six LVTH16244 devices. The trace is a 75- $\Omega$  transmission line. The receivers are separated by 1 cm, with the driver located in the center of the trace. Figure 17 and Figure 18 show the bus-hold loading effect on the driver when connected to six receivers switching low or high.

### **Bus-Hold Circuits**

www.ti.com

Figure 17 and Figure 18 also show the same system with the bus-hold circuit disconnected from the receivers. Both plots show the effect of bus hold on the driver's rise and fall times. Initially, the bus-hold circuit tries to counteract the driver, causing the rise or fall time to increase. Then, the bus-hold circuit changes states (note the crossover point), which helps the driver switch faster, decreasing the rise or fall time.

Figure 19 shows the supply current ( $I_{CC}$ ) of the bus-hold circuit as the input is swept from 0 to 5 V. The spike at about 1.5-V V<sub>1</sub> is due to both the N-channel and the P-channel conducting simultaneously. This is one of the CMOS transistor characteristics.

### Figure 19. Bus-Hold Circuit Supply Current Versus Input Voltage

The power consumption of the bus-hold circuit is minimal when switching the input at higher frequencies. Figure 20 and Figure 21 show the power consumed by the input at different frequencies, with or without bus hold. The increase in power consumption of the bus-hold circuit at higher frequencies is not significant enough to be considered in power calculations.

Figure 22 shows the data-sheet dc specifications for bus hold. The first test condition is the minimum current required to hold the bus at 0.8 V or 2 V. These voltages meet the specified low and high levels for TTL inputs. The second test condition is the maximum current that the bus-hold circuit sources or sinks at any input voltage between 0 V and 3.6 V (for low-voltage families) or between 0 V and 5.5 V (for ABT). The bus-hold current becomes minimal as the input voltage approaches the rail voltage. The output leakage currents,  $I_{OZH}$  and  $I_{OZL}$ , are insignificant for transceivers with bus hold because a true leakage test cannot be performed due to the existence of the bus-hold circuit. Because the bus-hold circuit behaves as a small driver, it tends to source or sink a current that is opposite in direction to the leakage current. This situation is true for transceivers with the bus-hold feature only and does not apply to buffers. All LVT, ABT Widebus+, and selected ABT octal and Widebus devices have the bus-hold feature (see Table 1 or contact the local TI sales office for more information).

Electrical Characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                                                                                                                                                                    | UMPHISK.      |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|

| V, = 0.8 V<br>Wor = <b>I</b> 3/℃, ALVC                                                                                                                             | 75            |  |  |

| $V_1 = 2$ V                                                                                                                                                        | -75           |  |  |

| Magana Matata de I/Os                                                                                                                                              | ± <b>þ</b> AO |  |  |

| V, = 0.8 V<br>₩हि⊺⊐∰i⊈eb/us+ and selectedABT                                                                                                                       | 100           |  |  |

| $V_1 = 2 V$                                                                                                                                                        | -100          |  |  |

| this test is not a true I <sub>NZ</sub> test because bus hold always is active on an I/O pin. Bu<br>transceivers with bus from<br>μ(λημε ομαριμμεταία age current. |               |  |  |

|                                                                                                                                                                    | цА            |  |  |

μΑ ΔBT Butschesstvishebtuschblettest since bus hold does not exist on an output pin. LVT, LVC, ALVC

Refer to the latest TI data sheets for device specifications.

### Figure 22. Example of Data-Sheet Minimum Specification for Bus Hold

hold tends to supply a current that is opposite in direction

# 5 Summary

Floating inputs and slow rise and fall times are important issues to consider when designing with CMOS and advanced BiCMOS families. It is important to understand the complications associated with floating inputs. Terminating the bus properly plays a major role in achieving reliable systems. The three methods recommended in this application report should be considered. If it is not possible to control the bus directly, and adding pull-up or pull-down resistors is impractical due to power-consumption and board-space limitations, bus hold is the best choice. TI designed bus hold to reduce the need for resistors used in bus designs, thus reducing the number of components on the board and improving the overall reliability of the system.

# IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated